# A 0.7V Time-based Inductor for Fully Integrated Low Bandwidth Filter Applications

Braedon Salz, M. Talegaonkar, G. Shu,

A. Elmallah, R. Nandwana,

B. Sahoo, P. K. Hanumolu

## **Outline**

- Motivation

- Proposed Architecture

- Circuit Implementation

- Measurement Results

- Summary

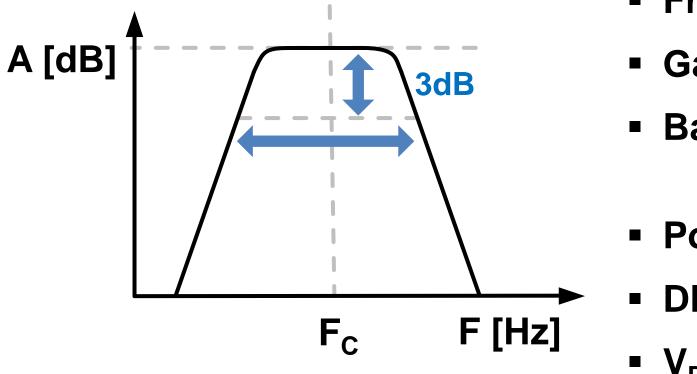

## Filter Metrics

- Frequency

- Gain

- **Bandwidth**

- Power

- DR

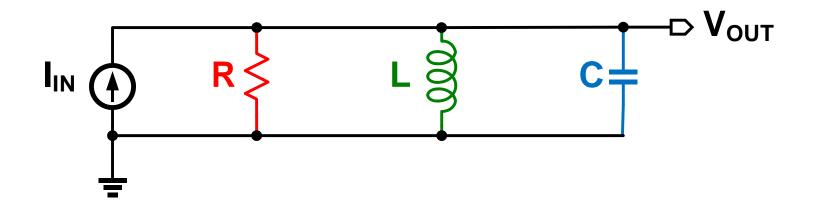

## Bandpass Filter Topology

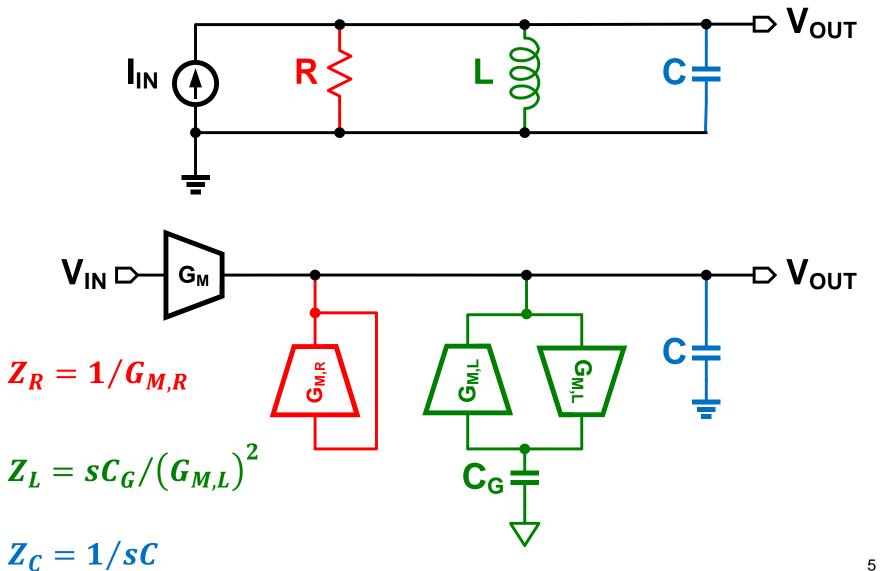

## Bandpass Filter Topology

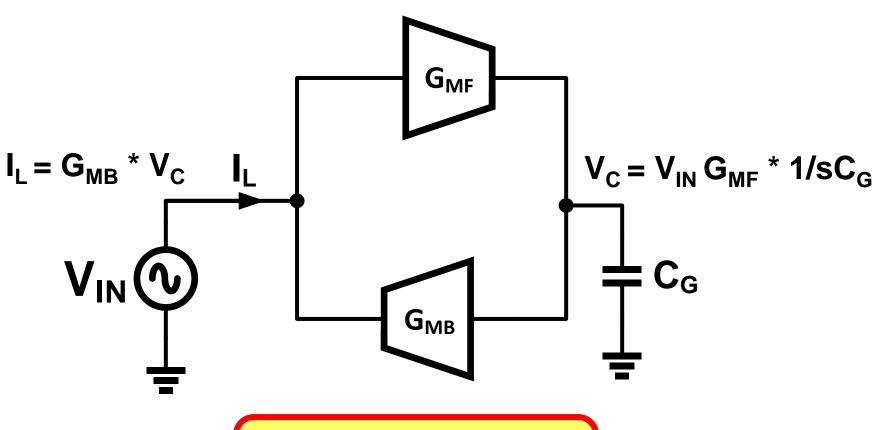

## Ideal Gyrator Circuit

$$Z_{IN} = \frac{sC_G}{G_{MB}G_{MF}}$$

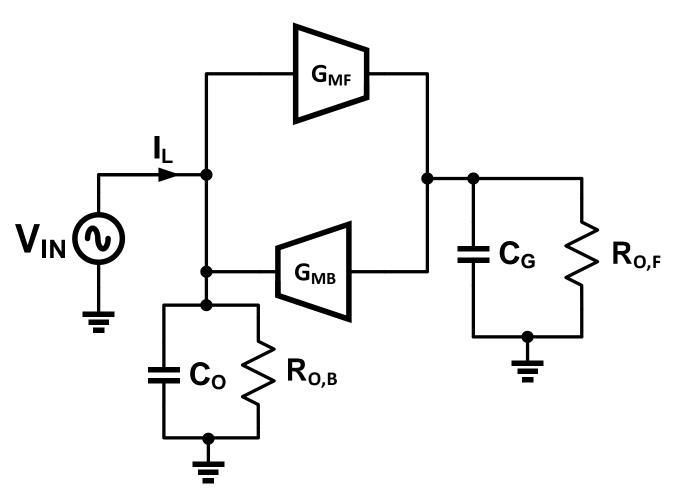

## Practical Gyrator

G<sub>M</sub> cells have finite output impedance

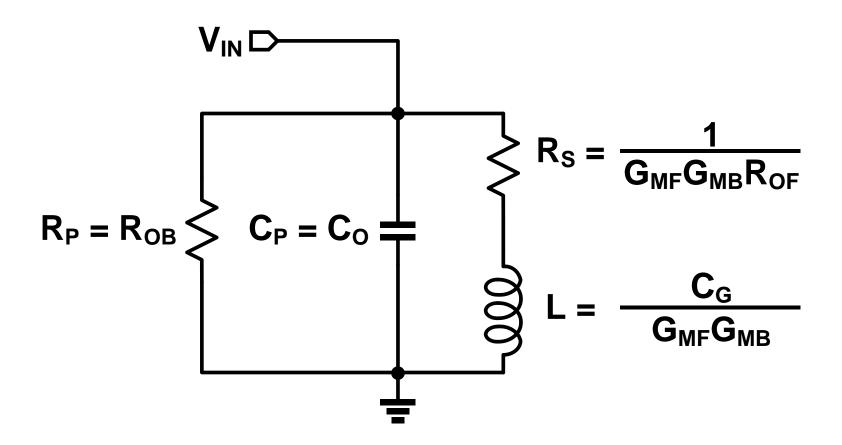

## Small Signal Gyrator Model

Gyrator can be viewed as RLC circuit

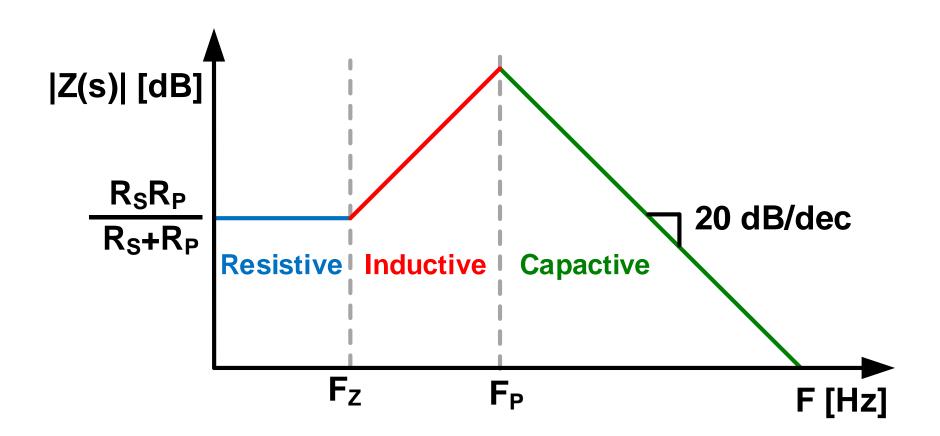

## Gyrator Transfer Function

# **Gyrator Quality Factor**

## Inductor Modeling

L scales inversely with integrator gain

Need a better integrator!

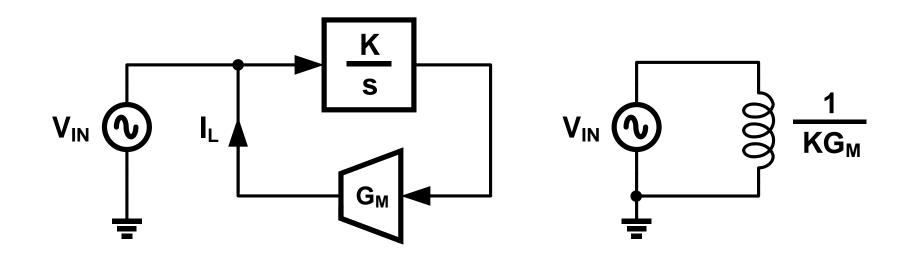

## Time-Based Integrator

$$K_{VCO} = \frac{F_{OUT}}{V_{IN}}$$

$$F_{OUT} = \frac{\partial \Phi_{OUT}}{\partial t} = s \; \Phi_{OUT}$$

$$H_{VCO}(s) = \frac{\Phi_{OUT}(s)}{V_{IN}(s)} = \frac{K_{VCO}}{s}$$

Oscillator is a V to  $\Phi$  integrator

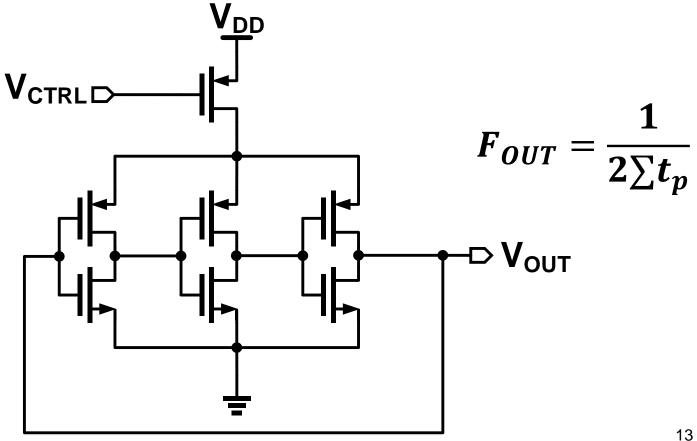

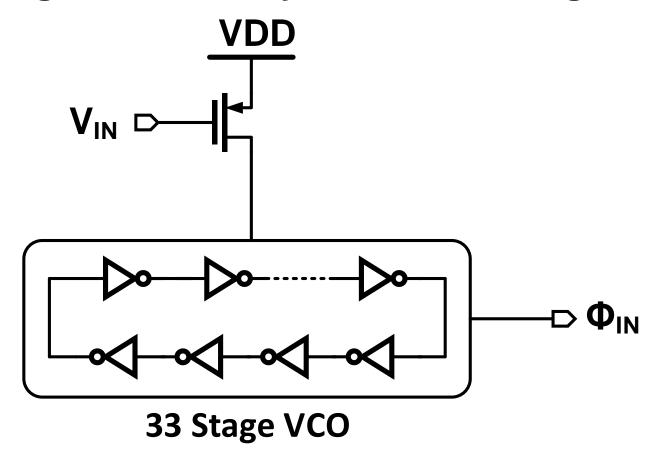

## Ring Oscillator

- V<sub>CTRI</sub> converted to current by PMOS

- Delay cells easily scalable, low area

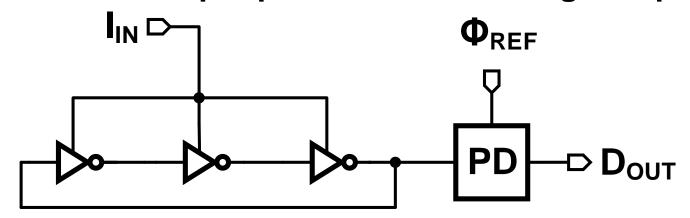

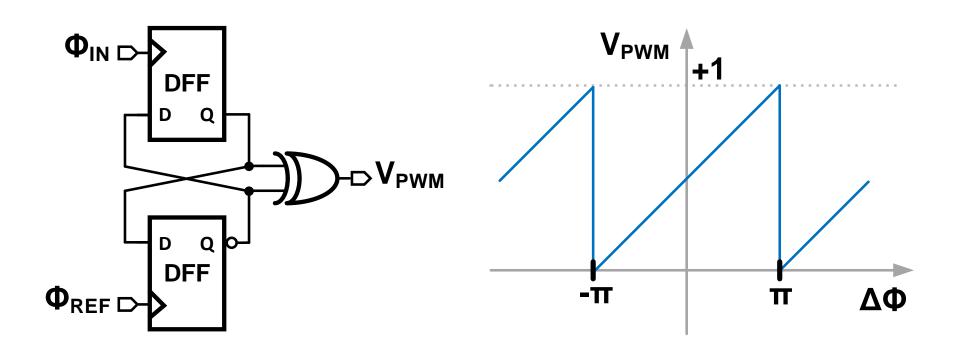

## Back to the Voltage?

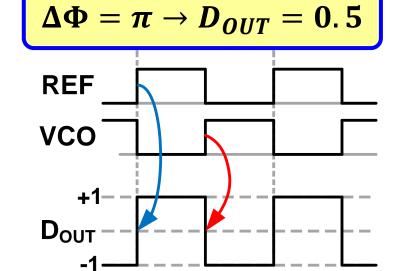

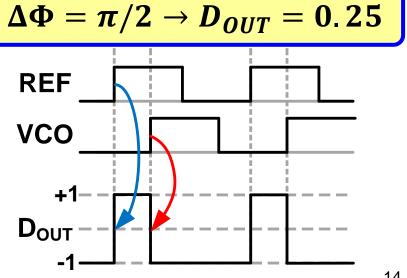

PD converts input phase to PWM voltage output

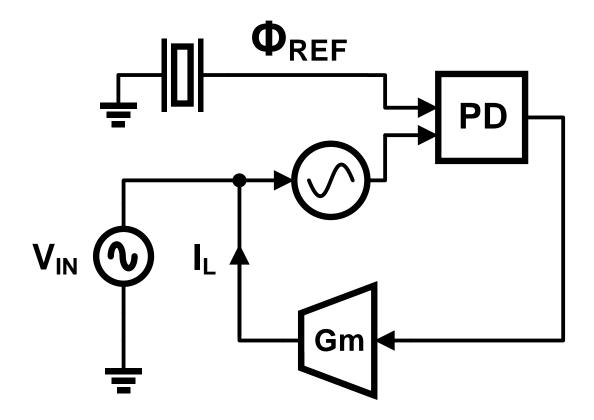

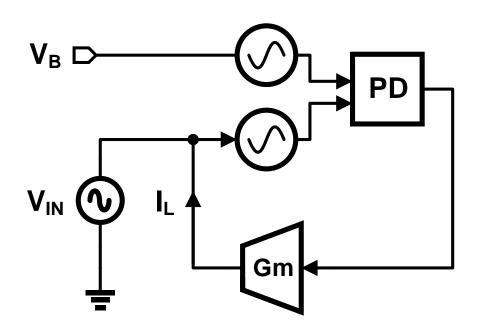

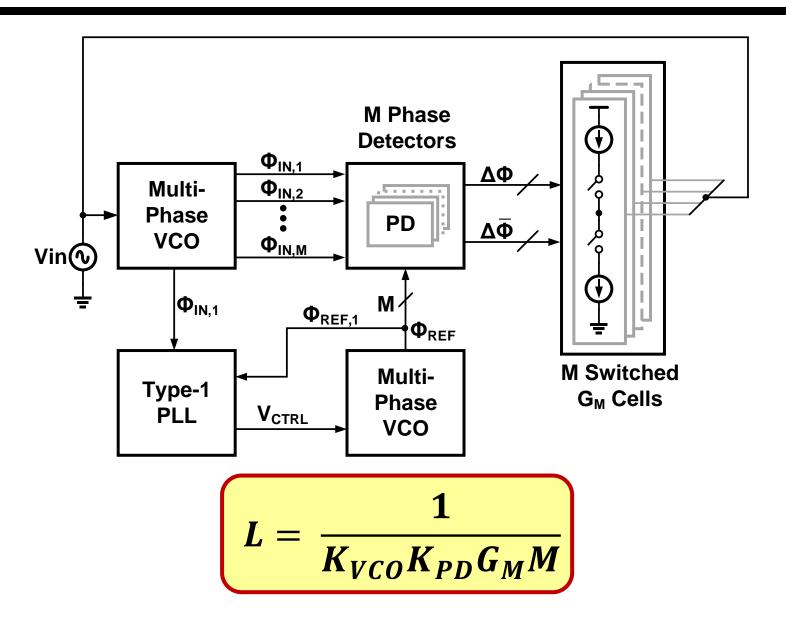

## Time-Based Inductor

## Time-Based Inductor

$$L = \frac{1}{K_{VCO}K_{PD}G_M}$$

# Effect of VCO F<sub>FR</sub> Mismatch

#### Any offset is continuously integrated

## PD Input Range

K<sub>PD</sub> has limited linear input range

$$V_{IN} = A\sin(\omega_{IN}t)$$

$$\Delta F = A K_{VCO}$$

$$\Delta \Phi = \frac{AK_{VCO}}{\omega_{IN}} \leq \Delta \Phi_{Max}$$

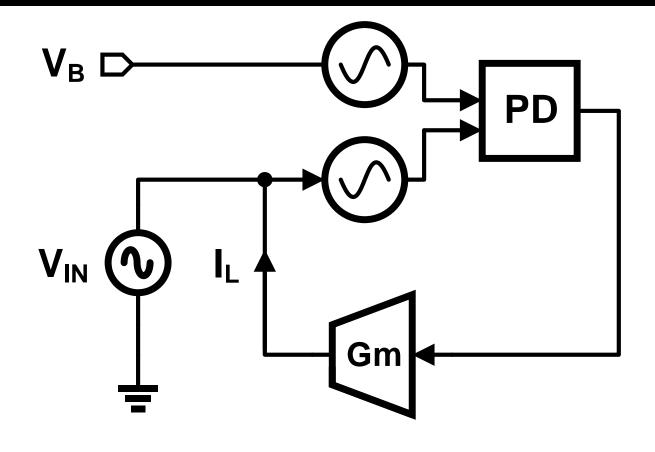

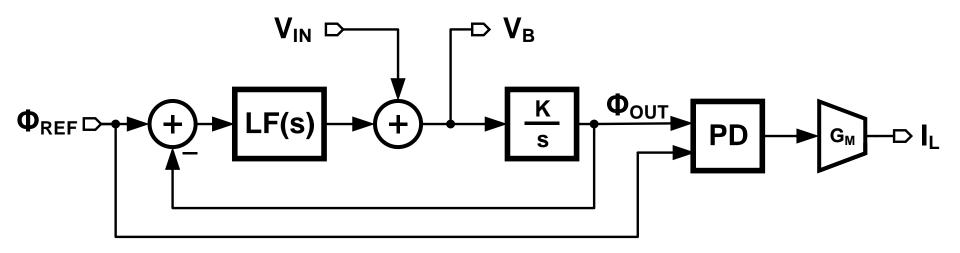

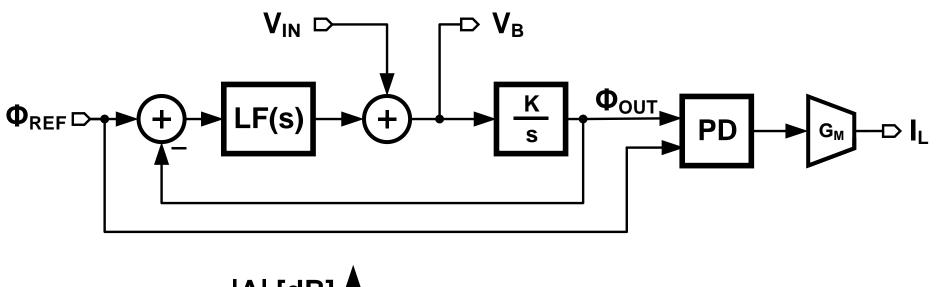

## Generating V<sub>B</sub>

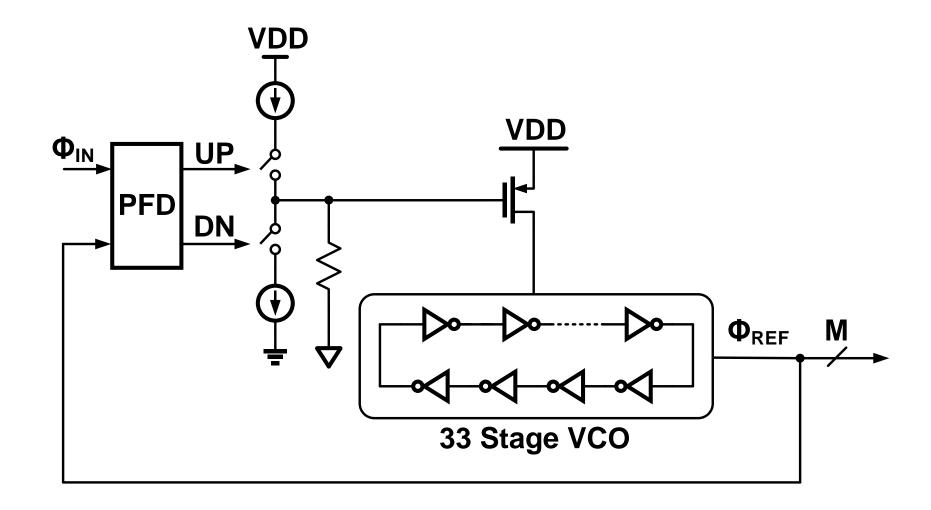

Use a PLL to limit low-frequency response

# Generating V<sub>B</sub>

20

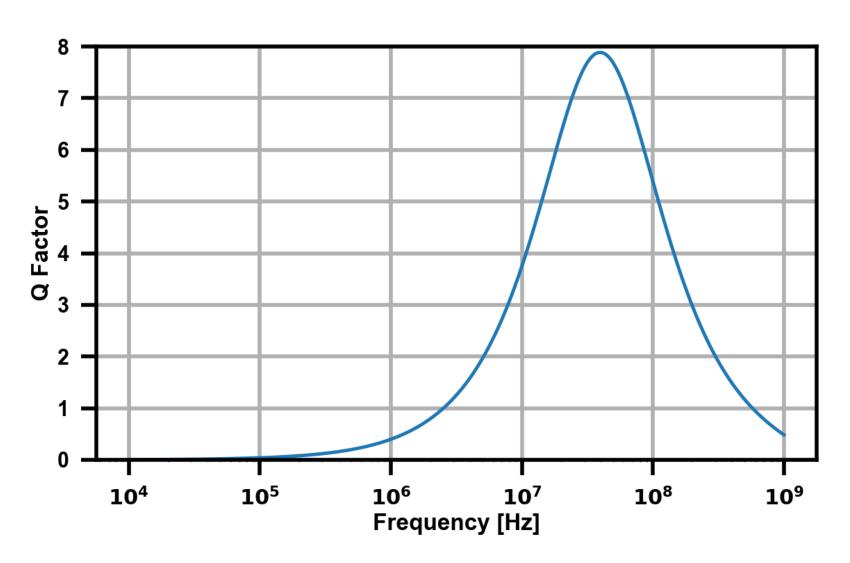

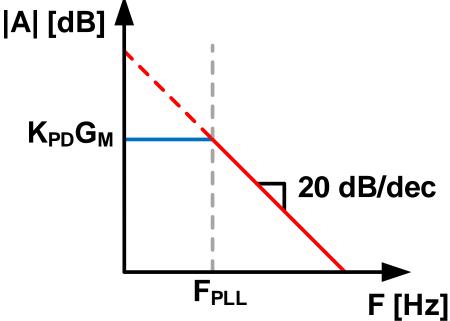

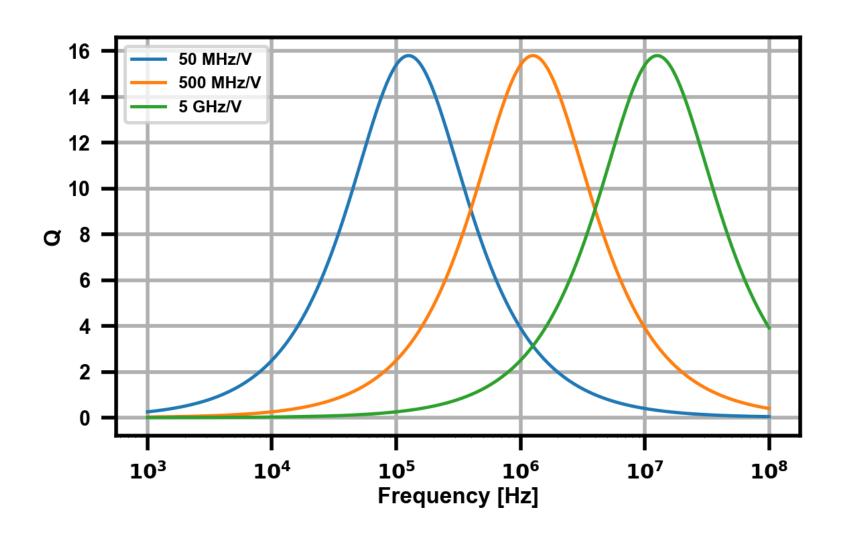

# Inductor Q vs K<sub>VCO</sub>

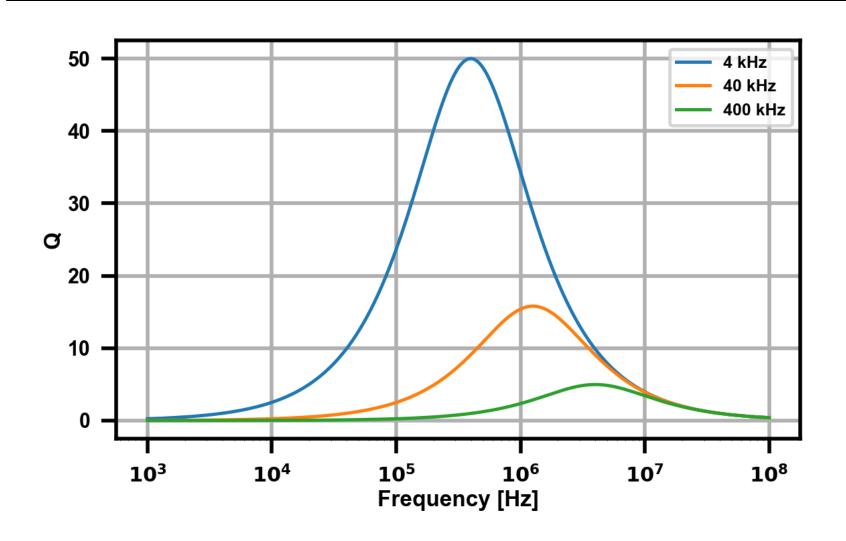

## Inductor Q vs PLL Bandwidth

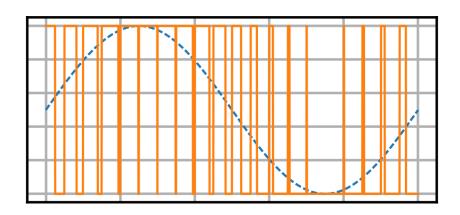

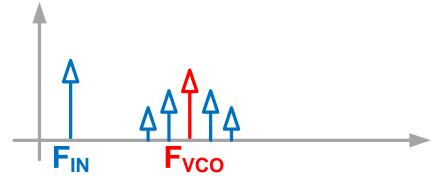

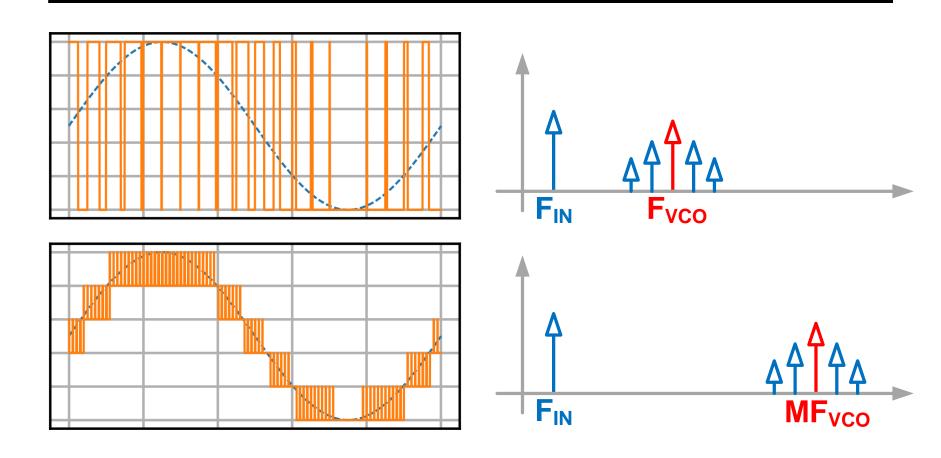

# Mitigating PWM Tones

# Mitigating PWM Tones

PWM tones move to MF<sub>VCO</sub>

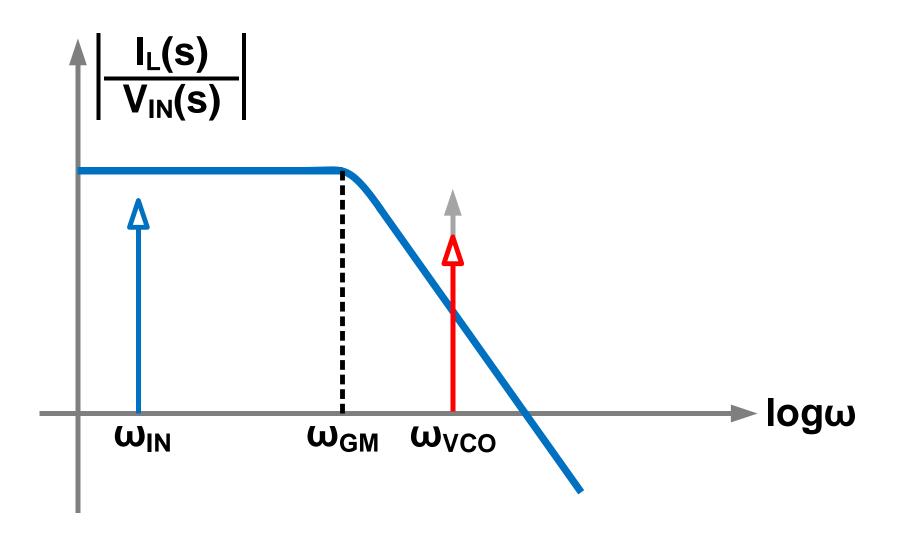

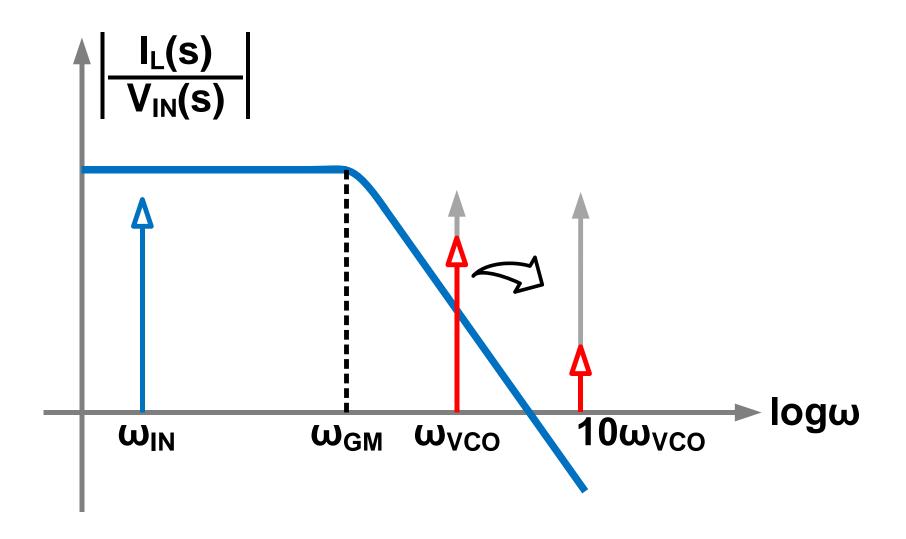

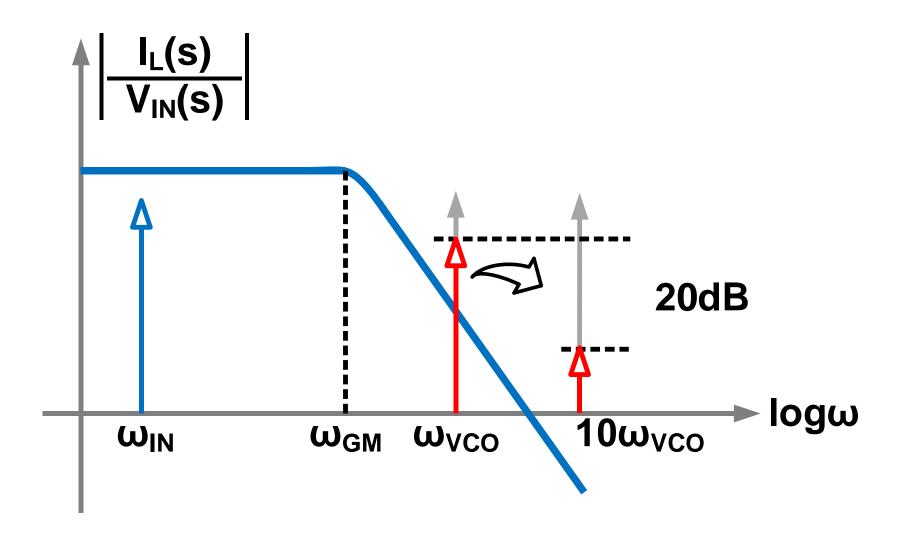

# Reducing Spurious Tones

# Reducing Spurious Tones

# Reducing Spurious Tones

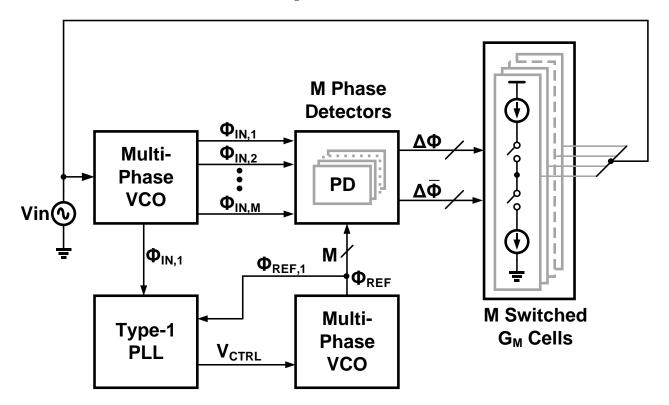

## Complete Architecture

## Voltage-Controlled Oscillator

- Each delay cell is an inverter

- Biasing controlled by current-limiting PMOS

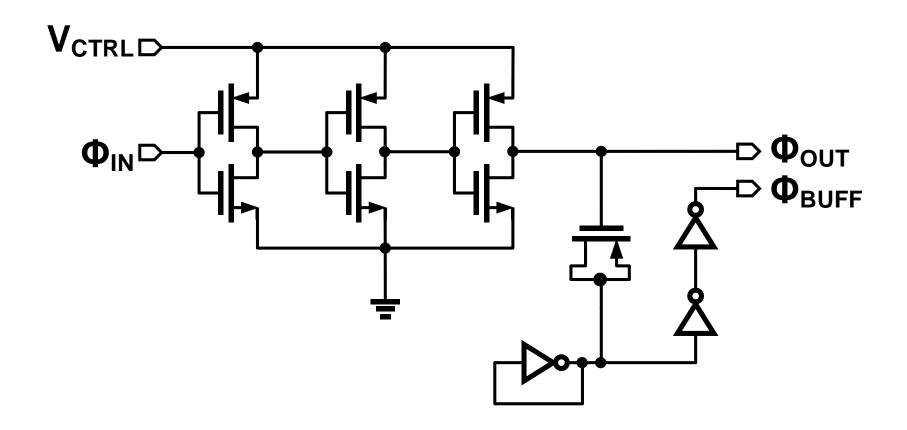

## Delay Cell

Need to bring output phase to full scale

## Phase Detector

• Two-state PD gives  $K_{PD} = 1/2\pi \text{ V/rad}$

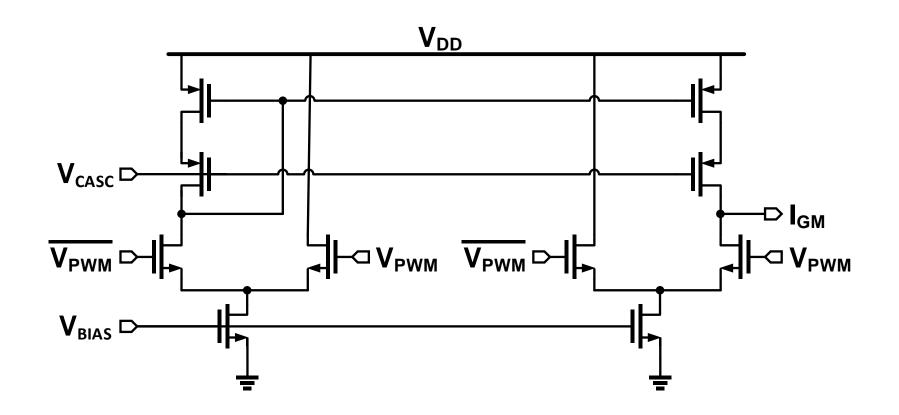

# Switched G<sub>M</sub> Cell

- Mirror G<sub>M</sub> used to match currents

- Diff pairs prevent transient discontinuities

# Type-I PLL

## Design Specifications

- K<sub>VCO</sub> tunable from 50 MHz/V 500 MHz/V

- G<sub>M</sub> tunable from 10 μA 50 μA / cell

- L tunable from 150 µH 1.5 mH

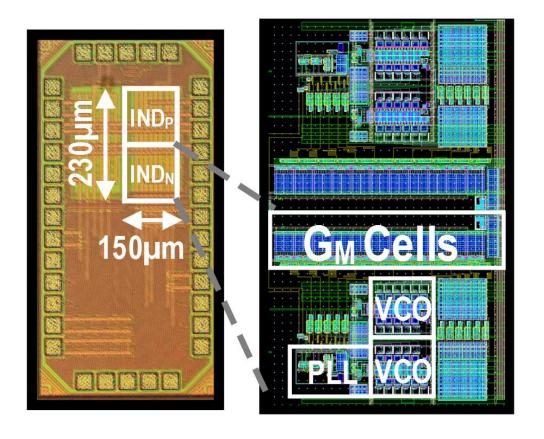

## Die Photo

- Fabricated in TSMC 65nm CMOS

- Inductor occupies 0.017 mm² area

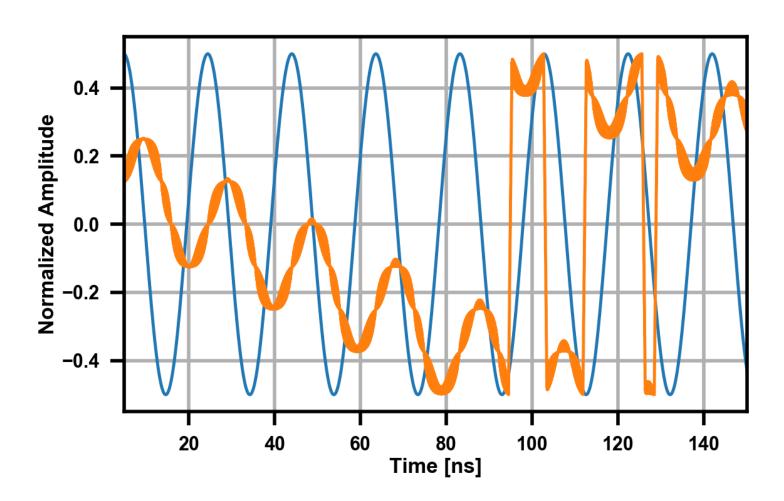

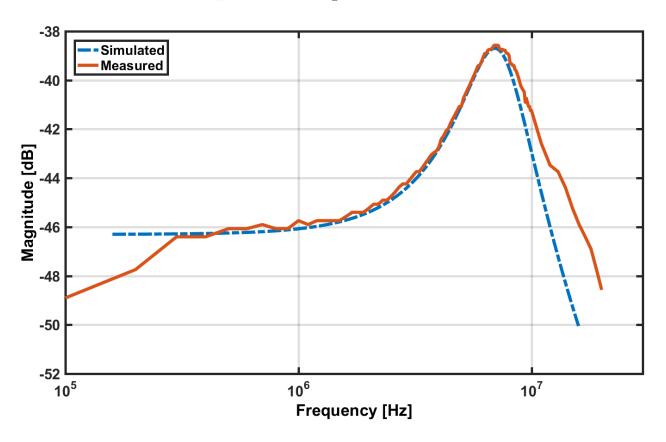

### Measurements

- Tested inductor in PCB passive filter

- Consumes 528µW of power

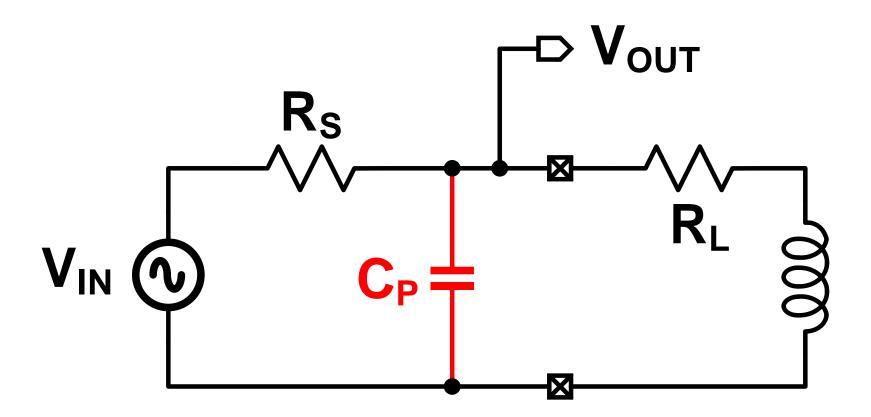

## Test Schematic

Results limited by parasitic capacitance

## Summary

Time-based inductor achieves significant area reduction

Highly digital design scales with process

Inductance value easily tunable

## Acknowledgements

Analog Devices Inc. for financial support

BDA for providing Analog Fast Spice (AFS) simulator